主存优化

知识预备

- DRAM 采用了电容作为存储元,使得主存每次进行读写时需要耗费一定的时间来刷新/恢复数据

- 假设 CPU 存取时间为 , 存取周期为 , 其中主存读取后的数据恢复时间为

目的

- 弥补 CPU 和主存直接的速度差异

优化方式

- 主存底层技术优化,减少主存数据恢复时间

- 采用多端口存储器

- 采用多体交叉存储技术

- 在 CPU 和主存之间插入高速缓冲存储器(Cache)

在此简要介绍 2 和 3

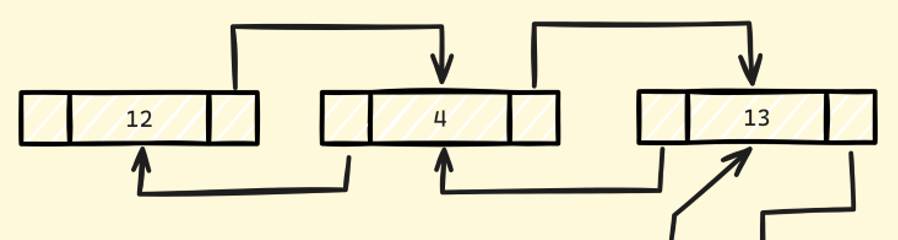

多端口存储器

以双端口存储器为例

- 特点

- 同一个存储器具体两组独立的读写控制电路,允许两个 CPU 异步访问存储单元

- 存储数据共享

- 当两个端口存取的地址不相同时,同时进行读写操作

- 当两个端口存取的地址相同,只要有一方写入,即发生读写冲突

- 发生冲突时,暂时关闭一个端口(置BUSY信号)

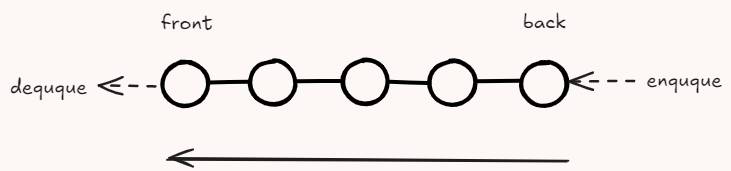

多体交叉存储

主存由多个存储模块组成,每个存储模块容量和存取速度相同,有单独的地址寄存器,数据寄存器,读写控制器和驱动电路

自我感觉和 主存扩展 结构相似

- 编址方式

- 顺序编址

- 仅扩容,不能提高速度

- 地址划分为: 模块号 | 模块内地址

- 交叉编址

- 连续访问时,在多个模块内切换,提高吞吐率

- 地址划分为: 模块内地址 | 模块号

- 顺序编址

交叉编址

- CPU 同时送出 m 个地址,若地址分别属于 m 个存储体,访问就不会冲突;交叉编址适合采用流水线方式并行存取

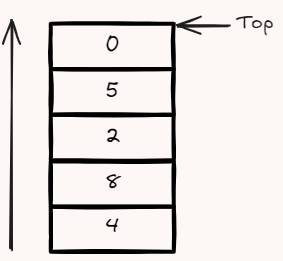

- 例: 预设总线传输时间为 , 存储周期为 , 模块数为 , 字长为

- 存取时间: 当 时,连续存取 个字的最短时间 (单体顺序编址存取时间 )

- 带宽: (单体顺序编址带宽 )

参考

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Forgotten Area!