主存

存储技术

| 类型 | 每位晶体管数 | 相对访问时间 | 持续的? | 敏感的? | 相对花费 | 应用 |

|---|---|---|---|---|---|---|

| SRAM | 6 | 1× | 是 | 否 | 1000× | 高速缓存存储器 |

| DRAM | 1 | 10× | 否 | 是 | 1× | 主存,帧缓冲区 |

地址译码方式

一维地址译码

- n 位地址, 条选择线

- 芯片容量增大时,译码器复杂度按指数规律增加

二维地址译码

- m 位行地址,n 位列地址,共 条选择线

- 相比一维地址编码更节省驱动器和译码线

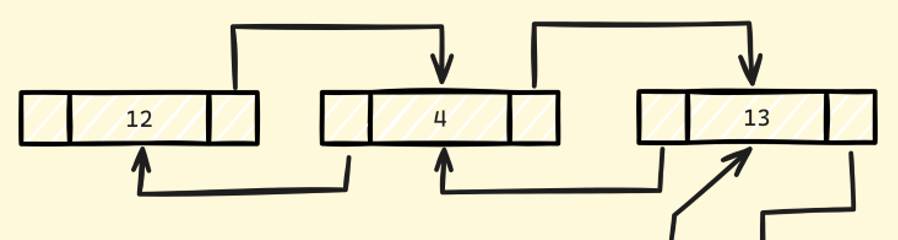

随机访问存储器

- 静态RAM(SRAM)

- 动态RAM(DRAM)

静态RAM(SRAM)

特点

- 使用双稳态触发器存储位数据(六管 MOS 静态存储器)

- 只要有电,就永远保持其值(静态)(存在干扰,当干扰消除时,电路会恢复到稳定值)

- 存取速度快,集成度低(容量小),价格高

- 常用作高速缓冲存储器 Cache

动态RAM(DRAM)

特点

- 使用半导体器件中分布电容上有无电荷来存储位数据(单管 MOS 静态存储器)

- 电源不掉电的情况下,信息也会丢失,因此需要不断刷新(存储单元大约在10~100ms内失去电荷,通过周期性读出、重写完成刷新)(当电压被扰乱后,就不会恢复了)

- 部分系统使用纠错码,对计算机的字多编几个位,来发现并纠正一个字中的存在的错误位

- 存取速度慢,集成度高(容量大),价格低

- 常用作内存条/图形系统的帧缓冲区

刷新机制

- 刷新周期: 从上一次刷新结束到下一次对整个DRAM全部刷新一遍为止的时间间隔

- 刷新操作: 按行执行内部的读写操作,刷新一行的所需时间为一个存取周期

- 单元刷新的间隔时间: DRAM 允许的最大信息保持时间,一般为2ms

- 刷新方式: 集中式刷新、分散式刷新和异步式刷新

只读存储器

- 只读存储器(Read-Only Memory)是一种只能读取指令和数据的存储器,即使是在关电后,仍然保存信息,属于非易失性存储器

- 在制造过程中,由存储器厂商或用户将指令和数据以一特制软件流程写入(烧录)到存储体中,该写入方法称为“编程”

- 存储在 ROM 设备中的程序通常被称为固件(firmware)。当一个计算机系统通电以后,它会运行存储在 ROM 中的固件(例如 BIOS 程序)

分类

ROM 是以它们能够被重编程(写)的次数和对它们进行重编程所用的机制来区分的

| 存储器 | 类别 | 擦除方式 | 能否单字节修改 | 写机制 |

|---|---|---|---|---|

| MROM | 只读 | 不允许 | 否 | 掩膜位写 |

| PROM | 写一次读多次 | 不允许 | 否 | 电信号 |

| EPROM | 写多次读多次 | 紫外线擦除,脱机改写 | 否 | 电信号 |

| E²PROM | 写多次读多次 | 电擦除,在线改写 | 能 | 电信号 |

| Flash Memory | 写多次读多次 | 电擦除,在线改写 | 否 | 电信号 |

- 掩膜式 ROM MROM(Masked ROM)

- 存储的信息由生产厂家在掩膜工艺过程"写入",用户无法修改

- 信息可靠性高,集成度高,适合大批量生产,价格便宜

- 可编程 ROM PROM(Programmable ROM)

- 芯片出厂时所有位为0,用户通过编程器熔断单元熔丝,即写入1

- 只能用高电流熔断一次(写入一次)

- 可擦写可编程 ROM EPROM(Erasable Programmable ROM)

- 紫外线照射“石英窗口”,使得浮栅内积存电子,管子内有导电沟道,所在位清零

- 通过特殊设备写入1

- 擦除和重编程次数数量级达1000次

- 电子可擦写可编程 ROM EEPROM(Electrically Erasable Programmable ROM)

- 类似 EPROM,但不需要物理上一个独立的编程设备,可直接在印制电路板上编程

- 编程次数数量级达 次

- 闪速存储器,闪存 Flash Memory

- 高密度非易失性的读/写存储器(存储容量大,可长期保存)

- 基于 EEPROM

主存扩展

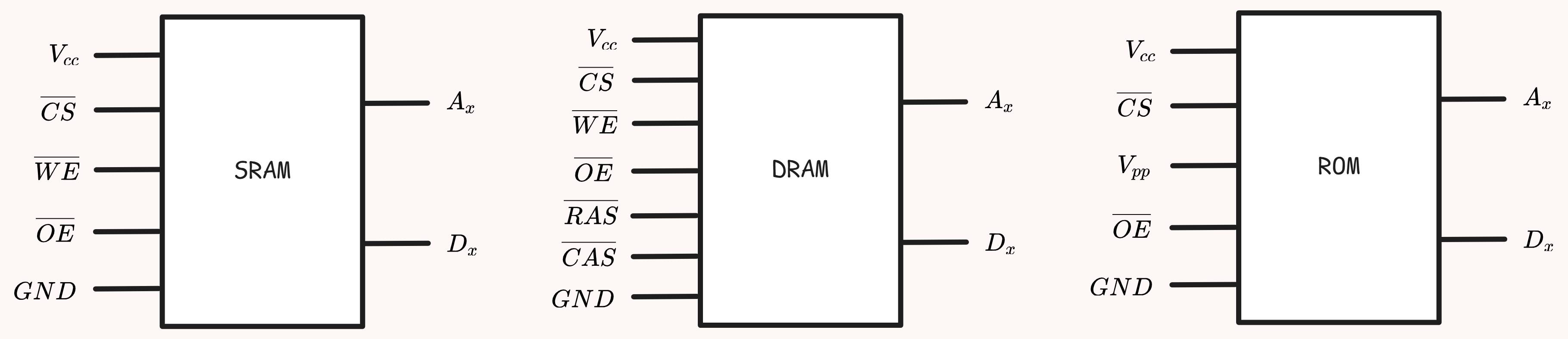

前提知识

芯片信号线组简要分类:

- 地址线

- 数据线

- 控制线

- 控制线组

- : 电路电源电压(高电平)

- : 擦除电压

- : 地线(低电平)

- : 片选信号(低电平有效)

- : 写使能信号(低电平有效)

- : 读使能信号(低电平有效)

- : 行地址选通信号(低电平有效)

- : 列地址选通信号(低电平有效)

- 其它(例如 时钟信号,图中没有列出来)

- 地址线组

- : 图中是简化的描述,地址线组可被描述为 ,占n个引脚

- 当数据地址有20位,但引脚不足20个时,需要复用地址引脚

- 地址线一般只用作输入

- 数据线组

- : 图中是简化的描述,地址线组可被描述为 ,占n个引脚

- 对于 RAM 而言,数据线可为输入和输出

- 对于 ROM 而言,数据线一般只作为输出,无法作为输入

扩展方式

- 位扩展: 增加字长来扩展容量

- 字扩展: 增加字的数量来扩展容量

- 字位扩展: 增加字长和字的数量来扩展容量

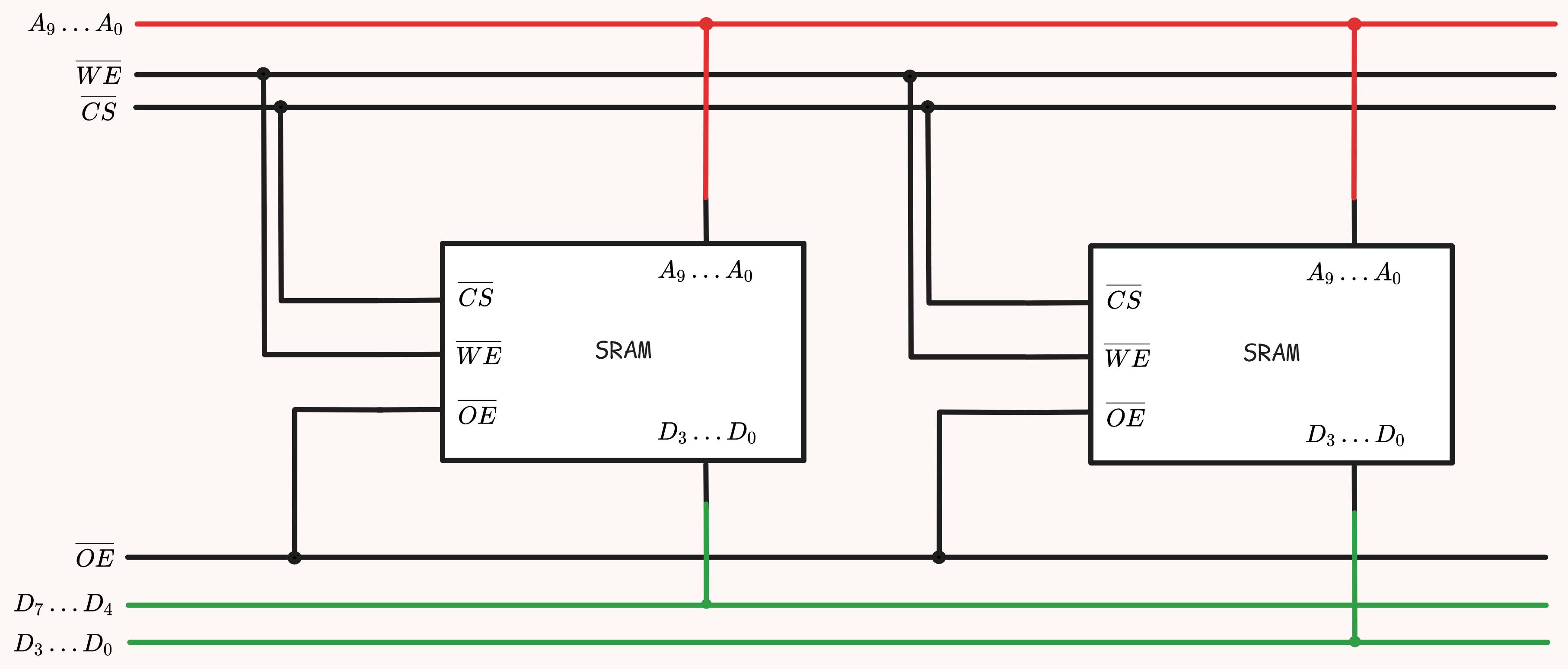

位扩展

- 要点

- 芯片的地址线,片选信号和读写信号与存储器相连

- 芯片的数据线分成多组,按一定次序分别连接在各个存储器上

- 例

- 问题: 用 1K * 4 位的SRAM芯片扩展成 1K * 8 位的SRAM存储器

- 分析: 芯片的地址线有10条(1K),数据线8条(8bit)

- 解答:

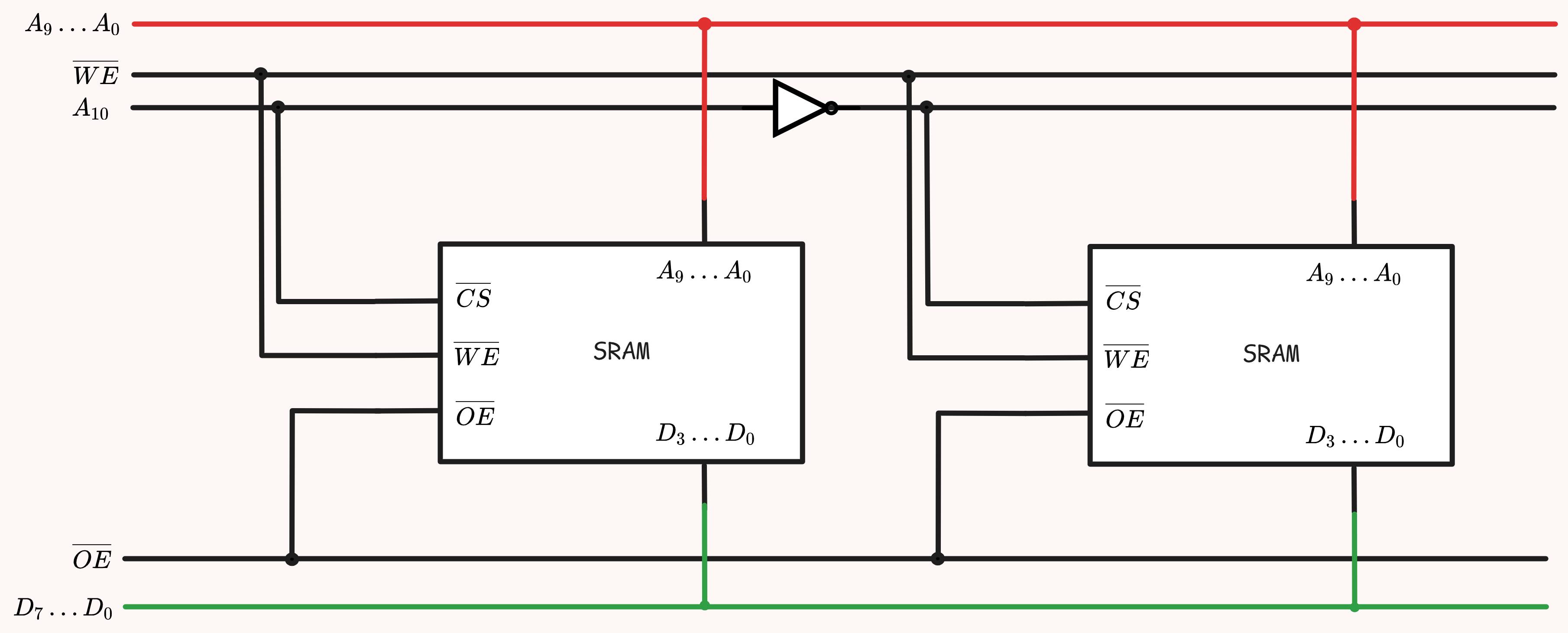

字扩展

- 要点

- 芯片的数据线,读写信号与存储器相连

- 芯片的地址线若干低位分成多组,按一定次序分别连接在各个存储器上

- 芯片的地址线若干高位连接片选信号

- 例

- 问题: 用 1K * 8 位的SRAM芯片扩展成 2K * 8 位的SRAM存储器

- 分析: 芯片的地址线有11条(2K),数据线8条(8bit)

- 解答:

字位扩展

- 预设: 需要扩展的存储器容量为 m * n 位,已有存储器芯片容量为 x * y (x < m, y < n)

- 要点

- m / x 组芯片进行字扩展

- 每组内 n / y 个芯片进行位扩展

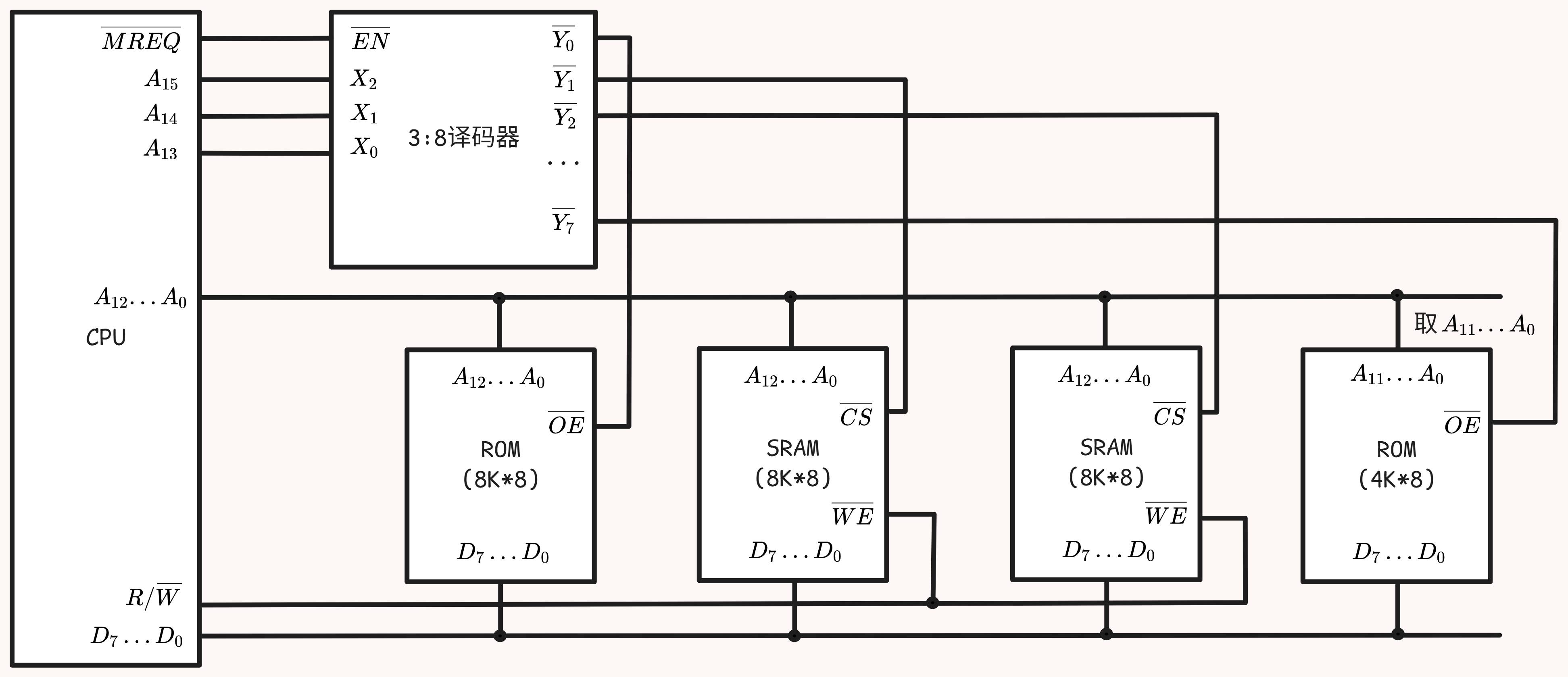

设计实例

问题

配置

- CPU

- 地址线 16 根( )

- 双向数据线 8 根( )

- 访存控制信号

- 读写控制信号

- 存储芯片

- 1K * 4位 SRAM

- 4K * 8位 SRAM

- 8K * 8位 SRAM

- 2K * 8位 ROM

- 4K * 8位 ROM

- 8K * 8位 ROM

- 其它

- 3:8 译码器及门电路

要求

- 最小 8K 地址为系统程序区(ROM区)

- 与其相邻的 16K 地址为用户程序区(RAM区)

- 最大 4K 地址空间为系统程序区(ROM区)

分析

- 数据位8位,地址位16位,寻址范围 ,将地址线高3位划分出来,用于片选,地址划分:

- 系统程序区1: 0x0000 ~ 0x0FFF

- 用户程序区: 0x1000 ~ 0x2FFF

- 系统程序区2: 0xF800 ~ 0xFFFF

- 芯片选取

- 选取1块芯片6完成要求1

- 选取2块芯片3完成要求2

- 选择1块芯片5完成要求3

- 连接

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Forgotten Area!